indie Semiconductor FFO GmbH Im Technologiepark 1 15236 Frankfurt (Oder) Germany

fon +49 335 / 228 80 30 fax +49 335 / 557 10 50 dfo.support@indiesemi.com

## TRA\_240\_097

240 GHz Highly Integrated Radar Transceiver with Antenna on Chip

## **Preliminary Datasheet**

| Status:     | Date:           | Author:                                 | Filename:              |         |

|-------------|-----------------|-----------------------------------------|------------------------|---------|

| Preliminary | 2025-02-11      | indie Semiconductor FFO GmbH            | Data Sheet TRX_240_097 |         |

| Version:    | Product number: | Package:                                | Marking:               | Page:   |

| 0.1         | TRX_240_097     | QFN 40 pin 5 x 5mm <sup>2</sup> package | TRA097                 | 1 of 20 |

### **Version Control**

| Version | Date          | Description of change | Reason for change |

|---------|---------------|-----------------------|-------------------|

| 0.1     | 11. Feb. 2025 | Creation of document  |                   |

|         |               |                       |                   |

|         |               |                       |                   |

### **Table of Contents**

| 1   | Features                           |    |

|-----|------------------------------------|----|

| 1.1 | Overview                           |    |

| 1.2 | Applications                       | 4  |

| 2   | Block Diagram                      | 5  |

| 3   | Pad Configuration                  | 6  |

| 3.1 | Pad Assignment                     | 6  |

| 3.2 | Pad Description                    | 6  |

| 4   | Specification                      |    |

| 4.1 | Absolute Maximum Ratings           | 8  |

| 4.2 | Operating Range                    | 8  |

| 4.3 | Thermal Resistance                 | 8  |

| 4.4 | Electrical Characteristics         | 9  |

| 4.5 | Power-up Sequencing                | 9  |

| 5   | Package                            |    |

| 5.1 | Outline dimensions                 |    |

| 5.2 | Package Code                       | 10 |

| 5.3 | Antenna Position                   | 11 |

| 6   | Application                        |    |

| 6.1 | Application Circuit Schematic      |    |

| 6.2 | Power Cycling                      | 12 |

| 6.3 | Evaluation Kit                     | 12 |

| 6.4 | Input / Output Stages              | 13 |

| 7   | Reliability and Environmental Test |    |

| 8   | Measurement Results                |    |

### **1** Features

- Radar front end (RFE) with on-chip antenna

- Wide bandwidth of 45 GHz in frequency band of ISM band at 245 GHz

- Integrated low phase noise VCO with injection locking feature

- External LO input

- Receiver with homodyne mixer

- Fully ESD protected device

- Chip can be cascaded in a massive MIMO system

- QFN 40 pin package, 5mm x 5mm with 0.4mm pitch, Pb-free, RoHS compliant

- Device is available as standalone integrated circuit,

- or on Radar Front End for evaluation with Evalkit Easy r4 and optionally with lens

#### 1.1 <u>Overview</u>

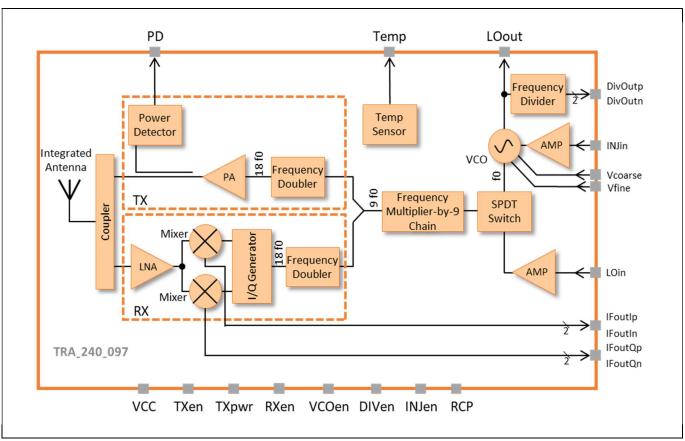

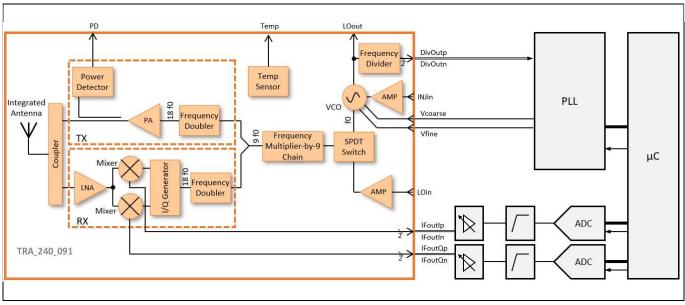

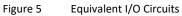

The radar front end TRA\_240\_097 is an integrated transceiver circuit for 240 GHz operation with on-chip antenna. It includes a voltage-controlled oscillator, divide-by-8 frequency divider, an SPDT switch, a frequency multiplier-by-9 chain, frequency doublers, mixers, a low-noise amplifier, a power amplifier, antenna-coupler and integrated antenna (see Figure 1). For proper functionality, a lens must be placed on top of the chip. The lens can be provided. The RF signal from the oscillator is amplified and fed to the frequency multiplier-by-9 chain, a doubler , and via a coupler to the integrated antenna. The RF signal from the oscillator is also directed to the RX path via amplifier and frequency doubler. The RX signal from the antenna is converted to baseband by a mixer with multiplied LO-signal. The 13.5 GHz VCO has two analog tuning inputs with different tuning ranges and tuning slopes. Both tuning inputs have to be used to obtain the wide RF frequency tuning range of 45 GHz. The analog tuning inputs together with the integrated frequency divider and external fractional-N PLL can be used for frequency modulated continuous wave (FMCW) radar operation. With fixed oscillator frequency it can be used in continuous wave (CW) mode. Other modulation schemes are possible as well by utilizing the analog tuning inputs. The chip can be fed with external LO signal. Many chips can be aligned in a massive MIMO system with external LO or daisy chained using on-chip VCO. The IC is fabricated in SG13G2 SiGe BiCMOS technology.

#### 1.2 Applications

The main field of application of the 240 GHz transceiver radar front end (RFE) is in short range radar systems which require high range resolution. 45 GHz of bandwidth theoretically gives a radar range resolution down to 6mm in air, and better than 6mm for other materials with refractive index higher than one. The range resolution is inversely proportional to the refractive index of the material.

The maximum range depends on the gain of the lens that is used, and it can reach several meters. By using lenses with higher gain, the range can be increased.

The RFE can be used in FMCW mode as well as in CW mode.

240 GHz IQ Transceiver TRA\_240\_097 Preliminary Datasheet Version 0.1 2025-02-11

# Indie

## 2 Block Diagram

Figure 1 Block Diagram of 240 GHz radar chip TRA\_240\_097.

240 GHz IQ Transceiver TRA\_240\_097 Preliminary Datasheet Version 0.1 2025-02-11

## Indie

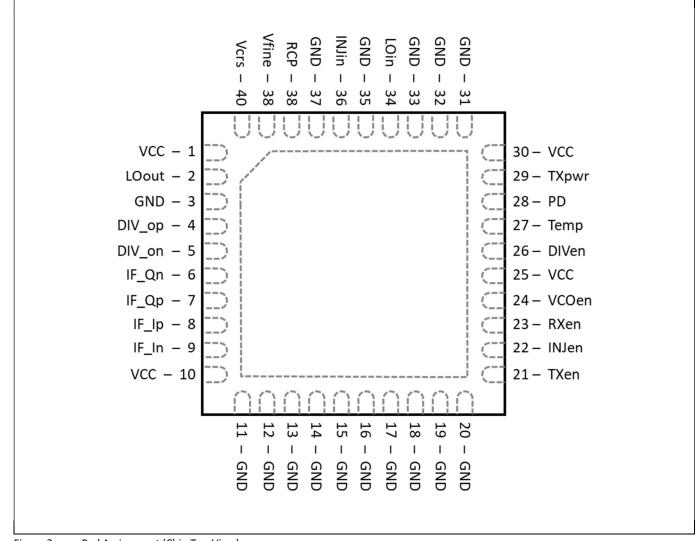

### **3** Pad Configuration

#### 3.1 Pad Assignment

Figure 2 Pad Assignment (Chip Top View)

TXen

#### 3.2 Pad Description

21

| Pin     |         | Description                                                                                                     |

|---------|---------|-----------------------------------------------------------------------------------------------------------------|

| No.     | Name    |                                                                                                                 |

| 1,10,25 | VCC     | Global Supply: 3.3 V                                                                                            |

| 2       | LOout   | VCO output RF-signal (single-ended 50 $\Omega$ ) (12-15 GHz), should be terminated with 50 $\Omega$ if not used |

| 4       | DivOutp | Divider output (differential 100 $\Omega$ ) (3-3.75 GHz), DC-coupled, on-board DC-block                         |

| 5       | DivOutn | capacitors are required                                                                                         |

| 6       | IF_Qn   | IF Q-output, DC-coupled                                                                                         |

| 7       | IF_Qp   | ANALOG Output: DC-coupled low impedance might damage the chip (> 500 $\Omega$ )                                 |

| 8       | IF_Ip   | IF I-output, DC-coupled                                                                                         |

| 9       | IF In   | ANALOG Output: DC-coupled low impedance might damage the chip (> 500 $\Omega$ )                                 |

TX-blocks (TX120 GHz Amplifier, TX-Doubler, TX-PA) control pin

DIGITAL: (3.3V for enable mode, 0V for disabled mode), 50 k $\Omega$  pull-down on chip

| INJen | VCO's injection Amplifier control voltage,                                                     |

|-------|------------------------------------------------------------------------------------------------|

|       | DIGITAL: (3.3V for enable mode, 0V for disabled mode), 50 k $\Omega$ pull-down on chip         |

| RXen  | RX-blocks (RX120 GHz Amplifier, RX-Doubler, RX-LNA, RX-IQ Mixers) control pin                  |

|       | DIGITAL: (3.3V for enable mode, 0V for disabled mode), 50 k $\Omega$ pull-down on chip         |

| VCOen | VCO and its Buffer Amplifiers control voltage, DIGITAL: (3.3V for enable mode –                |

|       | VCO is connected to multiplier, 0V for disabled mode – LOinput is connected to                 |

|       | multiplier), 50 kΩ pull-down on chip                                                           |

| DIVen | Divider control voltage, DIGITAL: (3.3V for enable mode, 0V for disabled mode), 50             |

|       | kΩ pull-down on chip                                                                           |

| Temp  | Temperature Sensor Output                                                                      |

|       | ANALOG Output: DC-coupled low impedance might damage the chip. (> 500 $\Omega$ )               |

| PD    | TX-Power Detector Output                                                                       |

|       | ANALOG Output: DC-coupled low impedance might damage the chip. (> 500 $\Omega$ )               |

| TXpwr | TX-Output Power Control                                                                        |

|       | ANALOG Input: Low impedance might damage the chip.                                             |

|       | 0V: P <sub>out_max</sub> , 3.3V: P <sub>out_max</sub> -16dB ; No pull-up/down resistor on chip |

| LOin  | External LO input (single-ended 50-ohm) (12-15 GHz), can be left open if not used              |

| INJin | 12-15 GHz VCO injection input signal (single-ended 50ohm), should be terminated                |

|       | with 50-ohm if not used                                                                        |

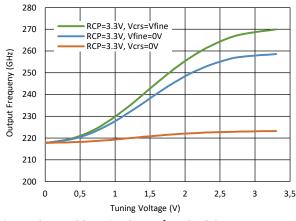

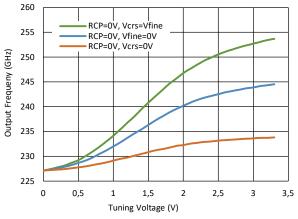

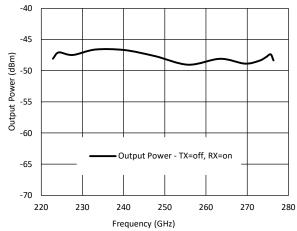

| RCP   | VCO Range control                                                                              |

|       | DIGITAL: (3.3V for 45 GHz, 0V for 23 GHz), 50k $\Omega$ pull-down on chip                      |

| Vfine | Fine frequency tuning voltage of VCO, 0V to 3.3V, ANALOG.                                      |

| Vcrs  | Coarse frequency tuning voltage of VCO, 0V to 3.3V, ANALOG.                                    |

| GND   | Global Ground. The IC's internal ground is connected to the exposed die attach pad             |

|       | of the QFN package. This pad must be soldered to PCB ground.                                   |

|       | RXen   RXen   VCOen   DIVen   Temp   PD   TXpwr   LOin   INJin   RCP   Vfine   Vcrs            |

### 4 Specification

#### 4.1 Absolute Maximum Ratings

Attempted operation outside the absolute maximum ratings of the part may cause permanent damage to the part. Actual performance of the IC is only guaranteed within the operational specifications, not at absolute maximum ratings.

#### Table 2Absolute Maximum Ratings

| Parameter                                                  | Symbol           | Min  | Max                   | Unit | Remarks / Condition                                         |

|------------------------------------------------------------|------------------|------|-----------------------|------|-------------------------------------------------------------|

| Supply voltage                                             | Vcc              |      | 3.6                   | V    | to GND                                                      |

| DC voltage at tuning inputs                                | Vvt              | -0.3 | V <sub>CC</sub> + 0.3 | V    | Inputs Vfine, Vcrs                                          |

| DC voltage at enable inputs                                | V <sub>EN</sub>  | -0.3 | V <sub>CC</sub> + 0.3 | v    | Inputs TXen, INJen, RXen, VCOen,<br>DIVen, TXpwr, RCP       |

| Junction temperature                                       | τ                | -50  | 150                   | °C   |                                                             |

| Storage temperature range                                  | T <sub>STG</sub> |      | 150                   | °C   |                                                             |

| Floor life (out of bag) at factory ambient (30°C / 60% RH) | FL               |      | 168                   | h    | IPC/JEDEC J–STD-033A MSL Level 3<br>Compliant <sup>1)</sup> |

| ESD robustness                                             | V <sub>ESD</sub> |      | 500                   | V    | Human body model, HBM <sup>2)</sup>                         |

1) If the devices are stored outside of the packaging, beyond this time limit, the device should be baked before use. The devices should be ramped up to a temperature of 125°C and baked for up to 12 hours.

2) CLASS 1A according to ESDA/JEDEC Joint Standard for Electrostatic Discharge Sensitivity Testing, Human Body Model Component Level, ANSI/ESDA/JEDEC JS-001-2011

#### 4.2 Operating Range

| Table 3 | Operating Range |

|---------|-----------------|

|         |                 |

| Parameter                   | Symbol          | Min  | Max             | Unit | Remarks / Condition                                   |

|-----------------------------|-----------------|------|-----------------|------|-------------------------------------------------------|

| Ambient temperature         | TA              | -40  | 65              | °C   |                                                       |

| Supply voltage              | Vcc             | 3.13 | 3.47            | V    | (3.3 V ± 5%)                                          |

| DC voltage at tuning inputs | V <sub>Vt</sub> | 0    | V <sub>cc</sub> | V    | Inputs Vfine, Vcrs                                    |

| DC voltage at enable inputs | V <sub>EN</sub> | 0    | 1.2             | V    | Inputs TXen, INJen, RXen, VCOen,<br>DIVen, TXpwr, RCP |

Note: Do not drive input signals without power supplied to the device.

#### 4.3 <u>Thermal Resistance</u>

#### Table 4 Thermal Resistance

| Parameter                                  | Symbol            | Min | Тур | Max | Unit | Remarks / Condition |

|--------------------------------------------|-------------------|-----|-----|-----|------|---------------------|

| Thermal resistance,<br>junction-to-ambient | R <sub>thja</sub> |     |     | 30  | K/W  | JEDEC JESD51-5      |

#### 4.4 <u>Electrical Characteristics</u>

$T_A = -40^{\circ}$ C to +65°C unless otherwise noted. Typical values measured at  $T_A = 25^{\circ}$ C and  $V_{CC} = 3.3$  V.

Table 5 Electrical Characteristics

| Parameter                               | Symbol                        | Min | Тур   | Max             | Unit   | Condition / Remark                |

|-----------------------------------------|-------------------------------|-----|-------|-----------------|--------|-----------------------------------|

| DC Parameters                           |                               |     |       |                 |        |                                   |

| Supply current consumption at $V_{CC1}$ | Icc1                          | tbd | 250   | tbd             | mA     | All enabled but INJEN<br>disabled |

| Enable input voltage,<br>Iow level      | V <sub>EN_L</sub>             | 0   |       | 0.3             | v      |                                   |

| Enable input voltage,<br>high level     | $V_{\text{EN}_{\text{H}}}$    | 2.7 | 3.3   | V <sub>cc</sub> | v      |                                   |

| VCO tuning voltage                      | Vvt                           | 0   |       | Vcc             | V      |                                   |

| RF Parameters                           |                               |     |       |                 |        |                                   |

| Start frequency                         | f⊤x                           | tbd | 222.5 | tbd             | GHz    |                                   |

| Stop frequency                          | f <sub>TX</sub>               | tbd | 267.5 | tbd             | GHz    |                                   |

| Tuning full bandwidth                   | Δf <sub>TX</sub>              | tbd | 45    | tbd             | GHz    |                                   |

| Pushing VCO                             | $\Delta f_{TX}/\Delta V_{CC}$ |     | Tbd   |                 | MHz/V  |                                   |

| Phase noise                             | P <sub>N</sub>                | tbd | -110  | tbd             | dBc/Hz | at 1 MHz offset, LOout            |

| Transmitter output power                | P <sub>TX</sub>               | tbd | 0.6   | tbd             | dBm    | Measured on-chip w/o<br>antenna   |

| Divider ratio of TX signal              | N <sub>div</sub>              |     | 72    |                 |        |                                   |

| Divider output power                    | P <sub>div</sub>              | tbd | -5    | tbd             | dBm    |                                   |

| Divider output start frequency          | f <sub>div</sub>              | tbd | 3.09  | tbd             | GHz    |                                   |

| Divider output stop frequency           |                               | tbd | 3.715 | tbd             | GHz    |                                   |

| Receiver gain                           | grx                           | tbd | 18    | tbd             | dB     | Measured on-chip w/o<br>antenna   |

| IF frequency range                      | f <sub>IF</sub>               | 0   |       | 100             | MHz    |                                   |

| IF output impedance                     | Zout                          |     | 50    |                 | Ω      | Differential outputs              |

| IQ amplitude imbalance                  | Aimb                          | tbd | 1     | tbd             | dB     |                                   |

| IQ phase imbalance                      | PHimb                         | tbd | 4     | tbd             | deg    |                                   |

| Noise figure (DSB)                      | NF                            | tbd | 15.7  | tbd             | dB     |                                   |

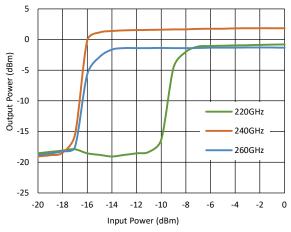

| Input compression point                 | 1dB ICP                       | tbd | -16.5 | tbd             | dBm    |                                   |

Note 1: Measured single-ended. Divider outputs are loaded with 50  $\Omega$ , external decoupling capacitors are required. No 50  $\Omega$  match is required in application.

#### 4.5 <u>Power-up Sequencing</u>

To prevent damage of IC at switching on or off a specific power-up and power-down sequence has to be followed. Reason is the special ESD-protection circuitry integrated in the chip with high-current diodes between control inputs/outputs and supply voltage pin(s) (see section ESD).

Power-up:

First, all supply voltages must be applied, and then apply control voltages.

Power-down:

First, switch off all control voltages, then switch off all supply voltages.

To meet the requirements, different sequencing techniques can be applied: sequential power-up, ratiometric power-up or simultaneous power-up. (See for example: <u>http://www.irf.com/technical-info/appnotes/an-1053.pdf</u>)

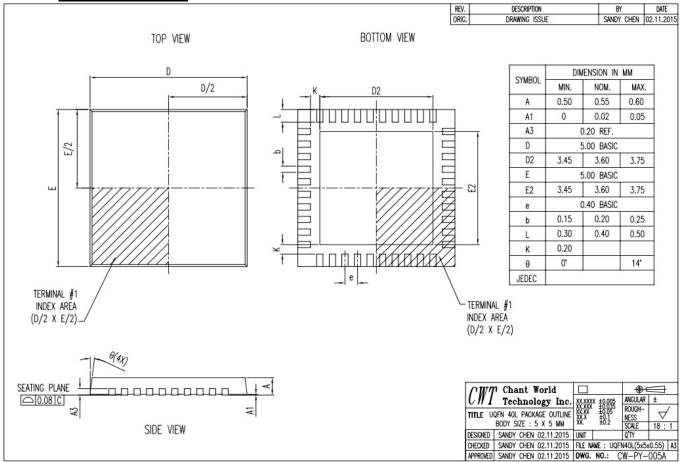

### 5 Package

#### 5.1 <u>Outline dimensions</u>

Figure 3 Outline Dimensions of QFN40 Package with Exposed Pad

#### 5.2 Package Code

Top-Side Markings TRA097 YYWW 240 GHz IQ Transceiver TRA\_240\_097 Preliminary Datasheet Version 0.1 2025-02-11

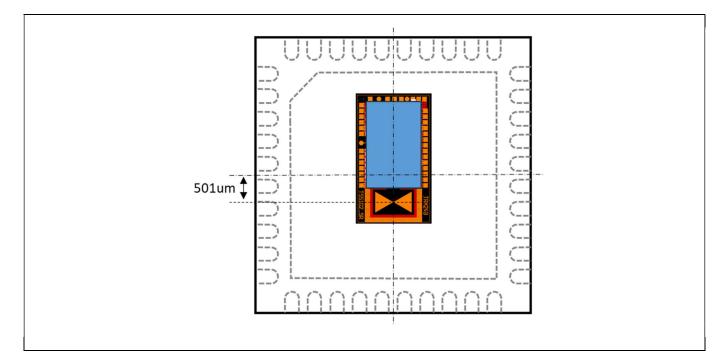

### 5.3 <u>Antenna Position</u>

The position of the radiating center of the integrated antenna is 501  $\mu$ m off the center of the 5 x 5 mm<sup>2</sup> package.

Figure 11 Antenna center vs. package center

### 6 Application

#### 6.1 Application Circuit Schematic

Figure 4 Application Circuit

#### 6.2 <u>Power Cycling</u>

It is possible to reduce power consumption by power cycling the radar front end. Rapid power cycling with voltage rise times between 10 and  $100\,\mu s$  is possible. At power-up, it must be ensured that no input signal is driven high before the supply voltage is stable. At power-down, all input signals must be pulled low before the supply voltage is switched off.

#### 6.3 Evaluation Kit

indie Semiconductor FFO offers evaluation kits for speeding up radar development. Please review our website and product sheets for more information: <u>https://www.indie.inc/radar-portfolio/#eval-kits</u>.

The SiRad Easy<sup>®</sup> r4 platform supports development for many of indie Semiconductor FFO integrated IQ transceivers including radar front end boards for TRA\_240\_097. It serves as reference hardware and provides a design environment including a graphical user interface for parameter setting. Its functionality and communication protocol are adaptable to development projects.

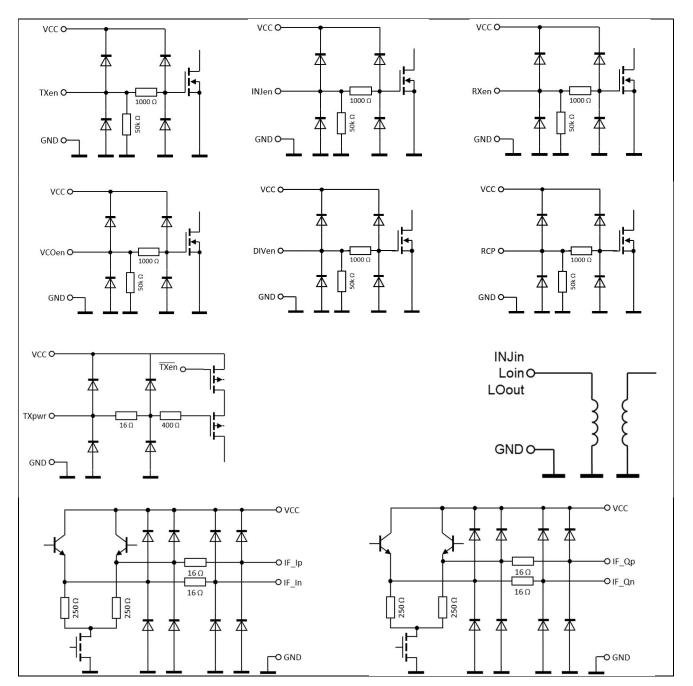

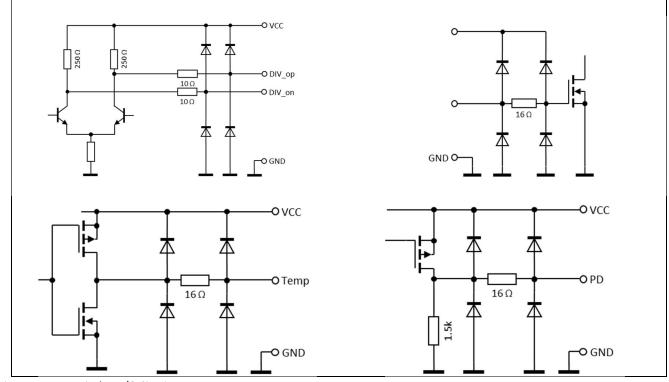

#### 6.4 Input / Output Stages

The following figures show the simplified circuits of the input and output stages. It is important that the voltage applied to the input pins never exceeds  $V_{CC}$  by more than 0.3 V. Otherwise, the supply current may be conducted through the upper ESD protection diode connected at the pin.

### 7 Reliability and Environmental Test

| Table 6Reliability and Environmental Test according to JEDEC Standards (performed for packaged device) |                |                                    |             |  |  |  |

|--------------------------------------------------------------------------------------------------------|----------------|------------------------------------|-------------|--|--|--|

| Qualification Test                                                                                     | JEDEC Standard | Condition                          | Pass / Fail |  |  |  |

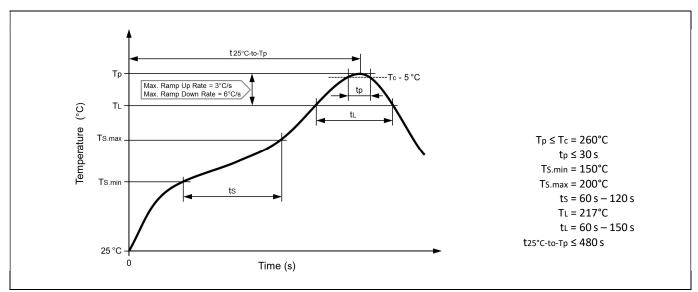

| MSL3                                                                                                   | J-STD-020E     | Reflow simulation 3 times at 260°C | tbd         |  |  |  |

| Temperature Cycling                                                                                    | JESD22-A104    | 850 cycles at -40°C 125°C          | tbd         |  |  |  |

| HTSL                                                                                                   | JESD22-A103    | 1,000 h at 150°C                   | tbd         |  |  |  |

| HTOL                                                                                                   | JESD22-A108    | 1,000 h at 85°C                    | tbd         |  |  |  |

| ТНВ                                                                                                    | JESD22-A101    | 1,000 h at 85°C and 85% RH         | tbd         |  |  |  |

| Figure 6 | Reflow Profile for Pb-Free Assembly according to JEDEC Standard J-STD-020E |

|----------|----------------------------------------------------------------------------|

| Figure o | Renow Frome for Fb-Free Assembly according to JEDEC Standard J-STD-020E    |

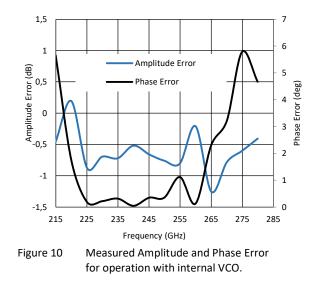

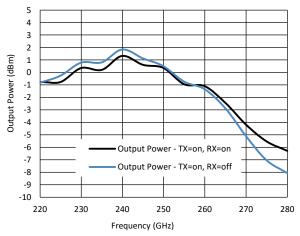

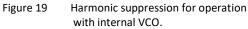

### 8 Measurement Results

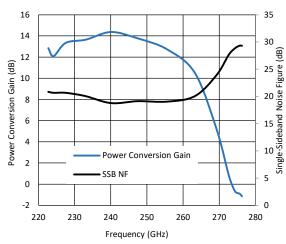

Figure 7 Power Conversion Gain and SSB Noise Figure for operation with internal VCO, measured at RX input (w/o antenna) for I-channel.

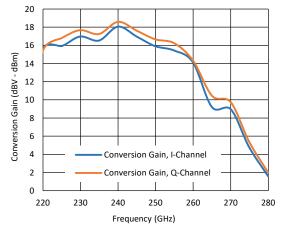

Figure 9 Conversion Gain for operation with internal VCO measured at antenna input.

Figure 8 Pow for c mea

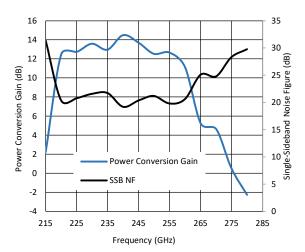

Power Conversion Gain and SSB Noise Figure for operation with external LO=0 dBm , measured at RX input (w/o antenna) for I-channel.

#### 20 18 16 Conversion Gain (dBV - dBm) 14 12 10 8 6 4 Conversion Gain. I-Channel Conversion Gain, Q-Channel 2 0 285 215 225 235 245 255 265 275 Frequency (GHz)

Conversion Gain for operation with external LO=0 dBm Figure 11 measured at antenna input measured at antenna input.

Figure 13 VCO Tuning Curves for RCP=3.3V.

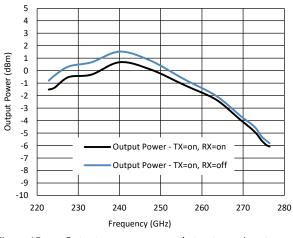

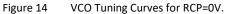

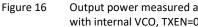

Figure 15 Output power measured at antenna input with internal VCO, TXEN=3.3V, TXpwr=0V.

ndie

Ir

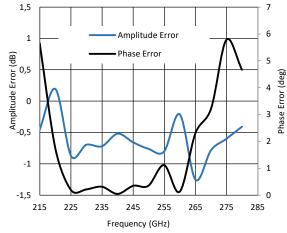

Measured Amplitude and Phase Error Figure 12 for operation with external LO=0 dBm.

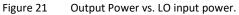

Output power measured at antenna input with internal VCO, TXEN=0V, TXpwr=0V.

Figure 17 Output power measured at antenna input with external LO=0 dBm, TXEN=3.3V, TXpwr=0V.

Ir

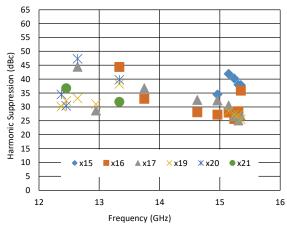

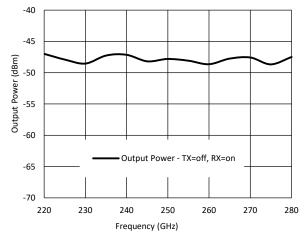

Harmonic suppression for operation with external LO=0 dBm.

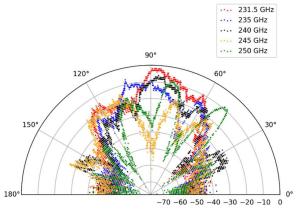

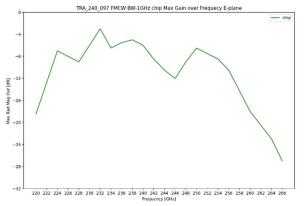

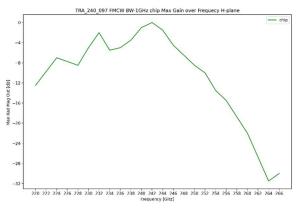

The combined normalized radiation patterns of RX and TX antenna for FMCW operation are shown in following figures. During the measurement, the IC was operated in FMCW mode with a bandwidth of 1 GHz. A corner reflector was used as the target. The frequency of the measurement refers to the start frequency of the sweep.

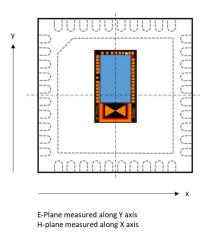

Figure 22 MMIC Orientation for Antenna Measurements.

TRA\_240\_097 FMCW E-pl BW=1GHz chip, Different Start Freq

Figure 23 Combined Radiation Pattern of TX and RX Antennas – E-plane.

Figure 25 Measured Maximum Normalize Gain for Combined TX and RX Antennas – E-plane.

90° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 120° 1

Figure 24 Combined Radiation Pattern of TX and RX Antennas – H-plane.

Figure 26 Measured Maximum Normalize Gain for Combined TX and RX Antennas – H-plane.

TRA\_240\_097 FMCW H-pl BW=1GHz chip, Different Start Freq

### Disclaimer

indie Semiconductor FFO GmbH 2025. The information contained herein is subject to change at any time without notice. indie Semiconductor FFO GmbH assumes no responsibility or liability for any loss, damage or defect of a product which is caused in whole or in part by

use of any circuitry other than circuitry embodied in an indie Semiconductor FFO GmbH product,

misuse or abuse including static discharge, neglect, or accident,

unauthorized modifications or repairs which have been soldered or altered during assembly and are not capable of being tested by indie Semiconductor FFO GmbH under its normal test conditions, or

improper installation, storage, handling, warehousing, or transportation, or

being subjected to unusual physical, thermal, or electrical stress.

Disclaimer: indie Semiconductor FFO GmbH makes no warranty of any kind, express or implied, with regard to this material, and specifically disclaims any and all express or implied warranties, either in fact or by operation of law, statutory or otherwise, including the implied warranties of merchantability and fitness for use or a particular purpose, and any implied warranty arising from course of dealing or usage of trade, as well as any common-law duties relating to accuracy or lack of negligence, with respect to this material, any indie Semiconductor product and any product documentation. Products sold by indie Semiconductor FFO GmbH are not intended to be used in life support applications or components, to operate nuclear facilities, automotive environments, or in other mission critical applications where human life may be involved or at stake. All sales are made conditioned upon compliance with the critical uses policy set forth below.

INDIE SEMICONDUCTOR FFO GMBH'S CONTRACTUAL AND NON-CONTRACTUAL LIABILITIES ARE STRICTLY LIMITED TO THE USE OF ITS PRODUCTS IN A SCOPE OF APPLICATIONS EXCLUDING THE OPERATION IN AUTOMOTIVE ENVIRONMENTS, LIFE SUPPORT DEVICES, NUCLEAR FACILITIES OR IN OTHER MISSION-CRITICAL APPLICATIONS OR COMPONENTS WHERE HUMAN LIFE OR PROPERTY MAY BE AT STAKE. AT ITS SOLE DISCRETION CUSTOMER MAY EXTEND THE FIELD OF APPLICATIONS ON CUSTOMER'S OWN RISK AND PERIL.

indie Semiconductor FFO GmbH owns all rights, titles and interests to the intellectual property related to indie Semiconductor FFO GmbH's products, including any software, firmware, copyright, patent, or trademark. The sale of indie Semiconductor FFO GmbH's products does not convey or imply any license under patent or other rights. indie Semiconductor FFO GmbH retains the copyright and trademark rights in all documents, catalogs and plans supplied pursuant to or ancillary to the sale of products or services by indie Semiconductor FFO GmbH. Unless otherwise agreed to in writing by indie Semiconductor FFO GmbH, any reproduction, modification, translation, compilation, or representation of this material shall be strictly prohibited.